動作合成とは?

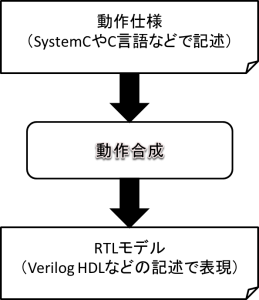

動作合成とは、所望の回路の動作を記述した動作仕様から、回路の構造を自動生成する技術のことである[改訂版EDA用語辞典 動作合成とは]。動作合成では、動作仕様の解析を行い、設計者が指定した設計制約を満たす回路を自動生成する。合成された回路は、レジスタ転送(RTL)モデルと呼ばれる表現として得られる。RTLモデルはハードウェア記述言語で記述される。現在の集積回路設計では、動作合成ツールは広く使われるようになってきた(例:Synopsys Synphony C Compiler、Cadence C-to-Silicon Compiler、Xilinx Vivado)。

動作合成の必要性

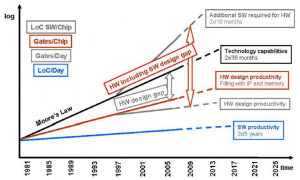

下図にITRSロードマップにて公表された設計で示された設計生産性と製造技術の関係を示す。

図中の黒線で表されるTechnology capabilitiesは、一つのチップ上に集積可能なトランジスタ数を表す。図中の赤線で表されるHW design productivityは、一人の設計者が一つのチップ上で実現可能な回路の規模を表す。上図に示されるように、設計者の設計能力と集積可能なトランジスタの数の間には、大きな開きがある。そして、その開きは今後、ますます大きくなっていくことが予想されている。このような設計規模の問題に対する解決策の一つとして、動作合成技術が提案されてきた。

動作合成のメリット

- アーキテクチャの検討が容易

- 動作合成では、設計者は所望の回路の動作仕様の記述を行う。動作合成が導入される前は、動作仕様からRTLモデルを生成するのも設計者が行っていたため、異なる条件のRTLモデルの生成を行うと時間がかかる、バグの混入により検証に時間がかかる、などの問題があった。しかし、動作合成を用いることにより、異なる条件のRTLモデルを生成するのは、動作合成ツールが行い、設計者は動作仕様の決定、合成されたRTLモデルの評価・検証を行うことになる。設計者は、同じ動作仕様から動作合成ツールを用いて異なるRTLモデルを生成し評価することで、どのRTLモデルを用いれば、要求された条件を満たすかを検証できる。

- 設計生産性の向上

- 動作合成では、設計者は回路の動作と構造ではなく、回路の動作を考えて設計を行う。そのため、回路の記述量がRTLモデルの設計よりも削減される。これは、設計期間の短縮というメリットがある。また、ここで設計される回路は動作のみが記述されているので、異なる回路で再利用することも容易となる。このような理由で、動作合成を用いることにより、設計生産性が向上する。

研究の背景

すでに述べたように、設計者の設計能力が集積回路に集積可能な設計規模に追いつかない、という問題を解決する方法の一つとして動作合成手法が提案されてきた。現在では、動作合成ツールが広く使われるようになってきた。しかしながら、これらの動作合成ツールは、クロック信号で回路の動作が制御される同期式回路を対象としている。集積技術の向上により、同期式回路ではクロック信号に起因する様々な問題が顕著となっている。たとえば、クロックスキューによる同期失敗、高周波数のクロック信号による消費電力の増大、電磁ノイズの増大、などの問題である。これに対して、要求信号と応答信号というローカルなハンドシェーク信号を用いて回路の動作を制御する非同期式回路では、クロック信号が存在しないため、これらの問題は発生しない。

非同期式回路には利点が多くあるが、非同期式回路の設計は難しいという欠点もある。非同期式回路の設計では、以下のような問題がある。

- ハザードフリーな回路が必要である。

- ハザードの伝搬により、回路の誤動作・停止が引き起こされてしまうため、ハザードのない回路が必要とされる。

- データエンコーディング方式、制御方式、遅延モデルによって異なる設計手法、設計制約が必要となる。

- 設計要求に応じて、データエンコーディング方式、制御方式、遅延モデルの選択を行い、設計しければならないため、熟練者でなければ、設計が難しい。

これらの理由に加えて、非同期式回路を対象とした動作合成手法が少ない、という問題がある。

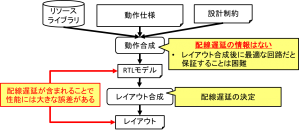

近年の集積技術の向上により、回路の性能において、論理遅延よりも配線遅延が支配的になってきている、という問題がある。このため、動作合成で最適な回路が得られたとしても、レイアウト設計後には最適ではなくなっている可能性がある(下の図を参照)。したがって、設計の早い段階で配線遅延の影響を考慮する必要がある。これまでに提案されている非同期式回路を対象とし動作合成手法では、配線遅延の影響が考慮されていない。

研究の目的

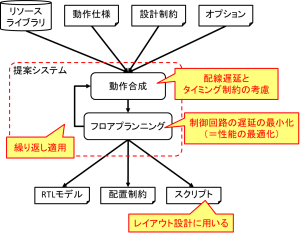

本研究では、束データ方式による非同期式回路を対象とした動作合成手法の提案を行う。本研究では、同期式回路を対象とした動作合成手法を基に、非同期式回路の特性を考慮した拡張を行う。以下に、本研究におけるポイントを示す。

- 非同期式回路の特性の考慮

- 束データ方式による非同期式回路のタイミング制約の考慮

- 配線遅延の考慮

上図に本研究で開発する動作合成システムの概要を示す。

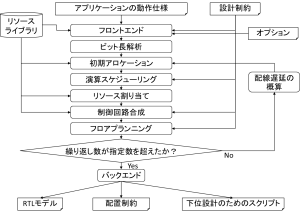

概要(設計フロー)

設計フローの流れを上図に示す。

入力

- アプリケーションの動作仕様

- C言語で記述されたアプリケーション

- リソースライブラリ

- リソースのパラメータとターゲットテクノロジを記述したXMLファイル

- リソースのパラメータ: 面積、遅延、入出力のビット長、など

- ターゲットテクノロジ: ASIC設計、FPGA設計、など

- リソースのパラメータとターゲットテクノロジを記述したXMLファイル

- 設計制約

- 設計制約(時間制約、資源制約)を記述したXMLファイル

- 時間制約とは、合成された回路が満たすべき性能のことを意味する。

- 資源制約とは、合成された回路が利用する資源の上限数のことを意味する。

- 設計制約(時間制約、資源制約)を記述したXMLファイル

- オプション

- その他、動作合成システムで用いる設定

- 関数展開

- メモリの利用

- コンパイラ・ディレクティブ

- その他、動作合成システムで用いる設定

出力

- RTLモデル

- 合成された束データ方式による非同期式回路をVerilog HDLで記述

- 配置制約

- フロアプランニングで決定された各モジュールの配置

- スクリプト

- 論理合成、レイアウト合成で用いるスクリプト

- ASIC設計、FPGA設計を対象にスクリプトは生成される。

- 論理合成、レイアウト合成で用いるスクリプト

手法の概要

- フロントエンド

- フロントエンドでは、与えられたアプリケーションの動作仕様の解析と中間表現であるControl Data Flow Graph (CDFG)を生成する。CDFGとは、アプリケーションのデータの流れと制御の流れを表したグラフである。

- フロントエンドは、COINSを用いて実現されている。

- ビット長解析

- ビット長解析を行うことで、適切なビット長のリソースの使用が可能となる。

- 面積の削減

- 性能の改善

- 以下のものを用いて、演算と変数のビット長の解析を行う。

- データ型(int、short、charなど)

- 入力と出力のビット長

- 演算の種類(加算、乗算、など)

- ビット長解析を行うことで、適切なビット長のリソースの使用が可能となる。

- 初期アロケーション

- 演算にリソースを割り当て、演算の実行時間を決定する。

- ここで、決定された実行時間を用いて演算スケジューリングを行う。

- 演算の実行時間の計算には、以下のものを用いる。

- 割り当てられたリソースの遅延時間(リソースライブラリで定義されている)

- フロアプラン結果から概算を行った配線遅延

- 前回のフロアプラン結果があれば配線遅延の概算結果を用いて、配線遅延の影響を考慮する。

- 前回のフロアプラン結果がない場合は、配線遅延は存在しないと仮定する。

- 演算にリソースを割り当て、演算の実行時間を決定する。

- 演算スケジューリング

- 演算の開始時間を決定する。

- キーポイント

- 非同期式回路では、演算の完了により次の演算が実行される。この性質を考慮して演算の開始時間を決定する。

- 束データ方式による非同期式回路のタイミング制約(分岐制約)を満たしやすくするように演算の開始時間を決定する。

- 時間制約下では、リソース数が最小となるようにする。

- Force-Directed Scheduling (FDS)アルゴリズムを拡張したAsynchronous FDSアルゴリズムを用いる。

- 資源制約下では、最速で動作するようにする。

- Force-Directed List Scheduling (FDLS)アルゴリズムを拡張したAsynchronous FDLSアルゴリズムを用いる。

- リソース割り当て

- 演算を演算器に、変数をレジスタに割り当て、データパス回路を生成する。演算器やレジスタが共有された場合には、適切な入力を選択するためにマルチプレクサの割り当ても行う。

- キーポイント

- ビット長の最小化

- マルチプレクサの削減

- 束データ方式による非同期式回路のタイミング制約(ホールド制約)の除去

- Left-Edgeアルゴリズムを拡張したExtended Left-Edgeアルゴリズムを用いる。

- 制御回路合成

- リソース割り当てで生成されたデータパス回路を制御する制御回路を生成する。

- 状態割当

- 演算スケジューリングから状態空間を決定する。

- Qモジュールの割り当て

- 一つの状態に対し、一つのQモジュールを割り当てる。

- データパス回路と制御回路のインターフェース生成

- 演算スケジューリングとリソース割り当ての結果から、データパス回路の各モジュールを制御するグルーロジックを生成する。

- 遅延素子の挿入とQモジュールの接続

- 状態から遅延時間を決定し、遅延素子を要求信号req上に挿入する。

- 状態遷移を導出し、次状態決定論理が必要であれば生成を行い、Qモジュールを接続する。

- フロアプランニング

- 合成された回路の各モジュールのチップ上での位置と形状を決定する。

- キーポイント

- 制御回路のレイテンシの最小化

- フロアプランニングを実行中に、タイミング制約を考慮

- 繰り返しのチェック

- 設計者が指定した回数を繰り返したかチェックする。

- 繰り返し数に到達していない場合には、初期アロケーションから再度実行する。

- キーポイント

- 繰り返し中に、レイテンシが最小のRTLモデルとフロアプランニング結果を保持

- バックエンド

- 合成された回路のRTLモデルを出力する。

- フロアプランニング結果から配置制約を出力する。

- リソースライブラリで指定されたターゲットテクノロジ情報に基づいて下位設計のためのスクリプトを生成する。

ポイント

同期式回路の場合、全ての演算はクロックサイクルタイム内で動作することが求められます。一方、束データ方式による非同期式回路では、各演算の実行時間は使用されるリソースの遅延や配線遅延によって決まります。この違いは、演算のスケジューリングにおける違いをもたらします。同期式回路の場合、あるクロックサイクルにおいて演算が処理を完了した際、クロックサイクルタイムまでの時間に余裕がない場合、次のサイクルまで次の演算の実行は待たされます。非同期式回路の場合、データやリソースの依存関係のある全ての演算が処理を終えたら、次の演算が実行可能となります。本研究で開発したツールは、こうしたことを考慮したうえでスケジューリングを行っています。

今後の課題

- 非同期式パイプライン回路の合成

- 同期式回路を対象とした動作合成手法では、スループットを向上させるためにパイプライン回路の合成を行う。しかしながら、本研究では、パイプライン回路の合成が行えていない。今後、非同期式パイプライン回路の動作合成手法の提案を行う。

- 低消費電力化手法の適用

- 本研究で開発されたツールで合成された非同期式回路に対し、低消費電力化手法を適用することにより、低消費電力な非同期式回路の合成が行えるようになる。

グラント

Publication

ジャーナル

- Naohiro Hamada and Hiroshi Saito, “Integration of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-Data Implementation”, IEICE Transaction, Volume E95-C No.4, pp.506–515, April 2012.

- Naohiro Hamada, Yuuki Shiga, Takao Konishi, Hiroshi Saito, Tomohiro Yoneda, Cris Myers, and Takashi Nanya, “A Behavioral Synthesis System for Asynchronous Circuits with Bundled-data Implementation”, IPSJ Transaction on System LSI Design Methodology, no.2, pp.67–79, Feburary 2009.

- Hiroshi Saito, Naohiro Hamada, Nattha Jindapetch, Tomohiro Yoneda, Cris Myers, and Takashi Nanya, “Scheduling Methods for Asynchronous Circuits with Bundled-Data Implementations Based on the Approximation of Start Times”, IEICE Transaction, vol.E90-A, no.12, pp.2790–2799, December 2007.

国際会議

- Naohiro Hamada and Hiroshi Saito, “Integration of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-data Implementation”, GLS VLSI’11 VLSI,pp.157–162, May 2011.

- Hiroshi Saito and Naohiro Hamada, “A floorplan method for asynchronous circuits with bundled-data implementation on FPGAs”, International Symposium on Circuits and Systems (ISCAS 2010),pp.925–928, May 2010.

- Naohiro Hamada, Hiroshi Saito, “Iterative Application of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-data Implementation”, The 24th International Technical Conference on Circuits/Systems, Computers and Communications,pp.53–56, July 2009.

- Naohiro Hamada, Yuuki Shiga, Hiroshi Saito, Tomohiro Yoneda, Cris Myers, and Takashi Nanya, “A Behavioral Synthesis System for Asynchronous Circuits with Bundled-data Implementation”, International Conference on Application of Concurrency to System Design, pp.50–55, June 2008.

- Takao Konishi, Naohiro Hamada, and Hiroshi Saito, “A Control Circuit Synthesis Method for Asynchronous Circuits in Bundled-Data Implementation”, International Conference on Compute and Information Technology, pp.847–852, October 2007.

- Hiroshi Saito, Nattha Jindapetch, Tomohiro Yoneda, Cris Myers, and Takashi Nanya, “ILP-Based Scheduling for Asynchronous Circuits in Bundled-Data Implementation”, International Conference on Compute and Information Technology, September 2006.

- Hiroshi Saito, Nattha Jindapetch, Tomohiro Yoneda, Cris Myers, and Takashi Nanya, “A Scheduling Method for Asynchronous Bundled-Data Implementations Based on The Completion of Data Operations”, International Technical Conference on Circuit/Systems, Computers and Communications, pp.433–434, July 2005.